# **Digital Comb Filter (NTSC)**

#### **Description**

The CXD2093Q is an adaptive intra-field three lines comb filter for NTSC systems, and can provide high-precision Y/C separation with a single chip.

#### **Features**

- · Adaptive intra-field three lines comb filter

- For NTSC

- Vertical enhancer

- · Horizontal aperture correction

- 8-bit A/D converter (1-channel)

- 8-bit D/A converter (2-channel)

- 4× PLL

- Sync tip clamp

#### **Applications**

Y/C separation for color TVs and VCRs

#### Structure

Silicon gate CMOS ICStructure

# **Absolute Maximum Ratings** (Ta = 25°C, Vss = 0V)

| <ul> <li>Supply voltage</li> </ul> | DVDD | Vss - 0.5 to +7.0 | V |

|------------------------------------|------|-------------------|---|

|                                    | DAVD | Vss - 0.5 to +7.0 | V |

|                                    | ADVD | Vss - 0.5 to +7.0 | V |

|                                    | PLVD | Vss - 0.5 to +7.0 | V |

|                                    | CLVD | Vss - 0.5 to +7.0 | V |

|                                    |      |                   |   |

- Input voltage

Vss 0.5 to Vdd + 0.5

Output voltage

Vss 0.5 to Vdd + 0.5

Vss 0.5 to Vdd + 0.5

- Storage temperature

Tstg -55 to +150 °C

#### **Recommended Operating Conditions**

| • Supply voltage                 | DVDD    | $5.0 \pm 0.25$ | V    |

|----------------------------------|---------|----------------|------|

|                                  | DAVD    | $5.0 \pm 0.25$ | V    |

|                                  | ADVD    | $5.0 \pm 0.25$ | V    |

|                                  | PLVD    | $5.0 \pm 0.25$ | V    |

|                                  | CLVD    | $5.0 \pm 0.25$ | V    |

| <ul> <li>Analog input</li> </ul> | ADIN    | 1.75           | Vp-p |

| Operating temp                   | erature |                |      |

|                                  | Topr    | -20 to +70     | °C   |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

SONY CXD2093Q

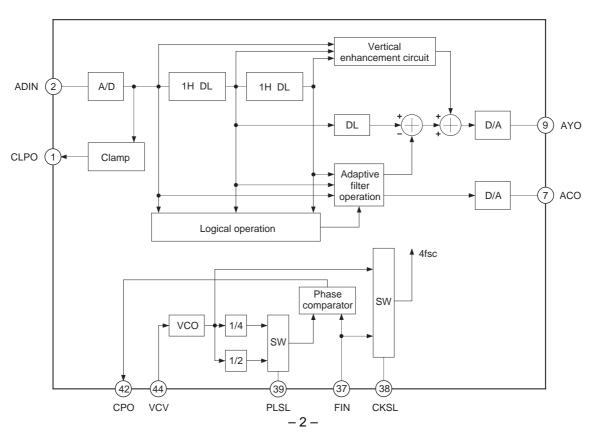

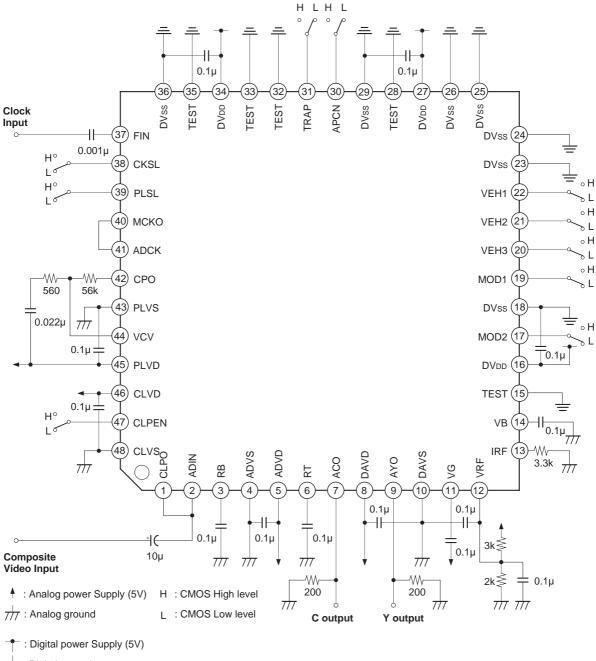

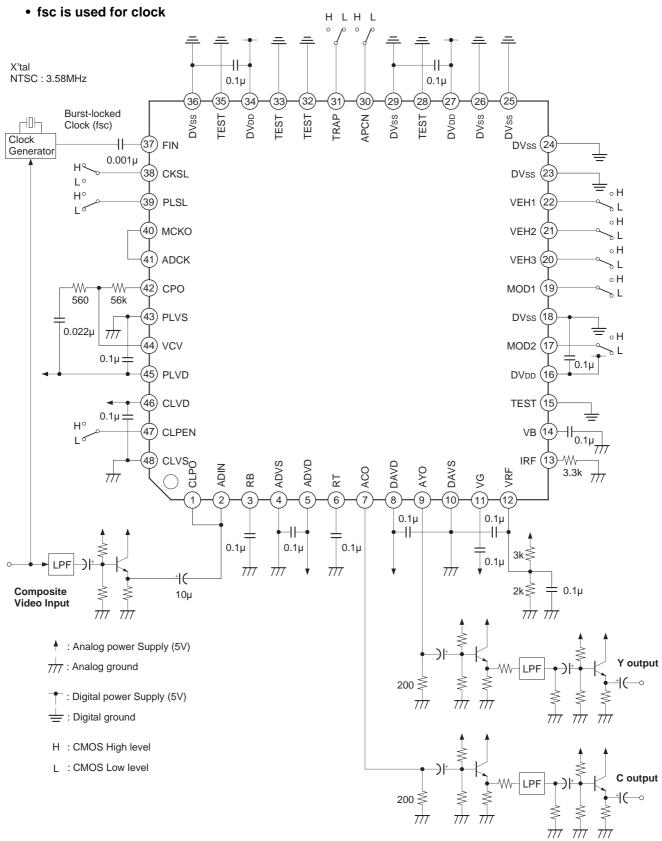

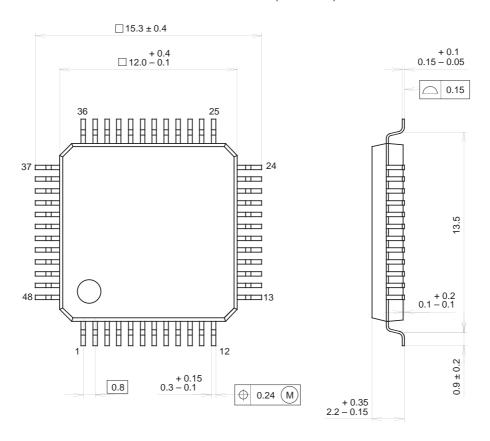

## **Pin Configuration**

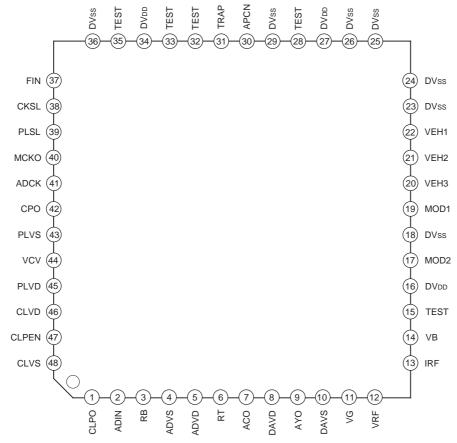

## **Block Diagram**

# **Pin Description**

| ground.  8 DAVD — D/A converter analog power supply. (5.0V)  9 AYO O Output can be obtained by connecting a resistor between this pin and the analog ground.  10 DAVS — D/A converter analog ground.  11 VG O D/A converter related pin. Connect a capacitor of approximately 0.1µF between this pin and the analog power supply (DAVD).  12 VRF I Sets the full-scale value of the Y and C-channel D/A converter output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin<br>No. | Symbol | I/O | Description                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-----|--------------------------------------------------------------------------------------|

| RB O Reference bottom voltage for the A/D converter (0.52V typ.).  ADVS — A/D converter analog ground.  ADVS — A/D converter analog ground.  ADVD — A/D converter analog power supply. (5.0V)  RT O Reference top voltage for the A/D converter (2.60V typ.).  ACO O Reference top voltage for the A/D converter (2.60V typ.).  ACO O Reference top voltage for the A/D converter (2.60V typ.).  ACO O Reference top voltage for the A/D converter (2.60V typ.).  ACO O Reference top voltage for the A/D converter (2.60V typ.).  ACO O D/A converter analog power supply. (5.0V)  Analog luminance signal output.  Output can be obtained by connecting a resistor between this pin and the analog ground.  DAVS — D/A converter analog ground.  11 VG O D/A converter analog ground.  12 VRF I Sets the full-scale value of the Y and C-channel D/A converter output signal.  13 IRF O Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter)  14 VB O D/A converter related pin.  Connect to the analog ground (DAVS) via a capacitor of approximately 0.1μF.  15 TEST I Test pin. Normally fix to "Low".  16 DVco — Digital power supply. (5.0V)  18 DVss — Digital ground.  17 MOD2 I Y/C separation mode setting. MOD2 MOD1  L L Adaptive processing mode H L BPF separation mode H L BPF separation mode H H Through mode  VeH3 I  Vertical enhancement setting.  Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  20 VEH3 I  Vertical enhancement setting.  Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1          | CLPO   | 0   | Connect to ADIN when using the internal clamp.                                       |

| 4 ADVS — A/D converter analog ground.  5 ADVD — A/D converter analog power supply. (5.0V)  6 RT O Reference top voltage for the A/D converter (2.60V typ.).  7 ACO O Seference top voltage for the A/D converter (2.60V typ.).  8 DAVD — D/A converter analog power supply. (5.0V)  Analog chroma signal output.  Output can be obtained by connecting a resistor between this pin and the analog ground.  8 DAVD — D/A converter analog power supply. (5.0V)  Analog luminance signal output.  Output can be obtained by connecting a resistor between this pin and the analog ground.  10 DAVS — D/A converter analog ground.  11 VG O D/A converter related pin. Connect a capacitor of approximately 0.1μF between this pin and the analog power supply (DAVD).  12 VRF I Sets the full-scale value of the Y and C-channel D/A converter output signal.  13 IRF O Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter)  14 VB O D/A converter related pin.  Connect to the analog ground (DAVS) via a capacitor of approximately 0.1μF.  15 TEST I Test pin. Normally fix to "Low".  16 DVpp — Digital power supply. (5.0V)  18 DVss — Digital ground.  17 MOD2 I Y/C separation mode setting. MOD2 MOD1  L L Adaptive processing mode  H L BPF separation mode  H L BPF separation mode  H H Through mode  20 VEH3 I Vertical enhancement setting.  Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  21 VEH2 I Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  22 VEH1 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2          | ADIN   | I   | Comb filter analog input (A/D converter input).                                      |

| 5 ADVD — A/D converter analog power supply. (5.0V) 6 RT O Reference top voltage for the A/D converter (2.60V typ.).  7 ACO O Reference top voltage for the A/D converter (2.60V typ.).  8 DAVD — D/A converter analog power supply. (5.0V)  9 AYO O Analog luminance signal output.  Output can be obtained by connecting a resistor between this pin and the analog ground.  10 DAVS — D/A converter analog ground.  11 VG O D/A converter related pin. Connect a capacitor of approximately 0.1μF between this pin and the analog power supply (DAVD).  12 VRF I Sets the full-scale value of the Y and C-channel D/A converter output signal.  13 IRF O Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter)  14 VB O D/A converter related pin. Connect a capacitor of approximately 0.1μF.  15 TEST I Test pin. Normally fix to "Low".  16 DVob — Digital power supply. (5.0V)  18 DVss — Digital ground.  17 MOD2 I Y/C separation mode setting. MOD2 MOD1  L L Adaptive processing mode H L BPF separation mode | 3          | RB     | 0   | Reference bottom voltage for the A/D converter (0.52V typ.).                         |

| 6 RT O Reference top voltage for the A/D converter (2.60V typ.).  Analog chroma signal output. Output can be obtained by connecting a resistor between this pin and the analog ground.  B DAVD — D/A converter analog power supply. (5.0V)  Analog luminance signal output. Output can be obtained by connecting a resistor between this pin and the analog ground.  D/A converter analog ground.  D/A converter related pin. Connect a capacitor of approximately 0.1μF between this pin and the analog power supply (DAVD).  VRF I Sets the full-scale value of the Y and C-channel D/A converter output signal.  RRF O Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter)  D/A converter related pin. Connect to the analog ground (DAVS) via a capacitor of approximately 0.1μF.  TEST I Test pin. Normally fix to "Low".  Digital power supply. (5.0V)  RDP Digital ground.  Vertical enhancement setting. Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  Vertical enhancement setting. Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  Digital ground.  Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4          | ADVS   | _   | A/D converter analog ground.                                                         |

| Analog chroma signal output. Output can be obtained by connecting a resistor between this pin and the analog ground.  B DAVD — D/A converter analog power supply. (5.0V)  Analog luminance signal output. Output can be obtained by connecting a resistor between this pin and the analog ground.  DAVS — D/A converter analog ground.  D/A converter related pin. Connect a capacitor of approximately 0.1μF between this pin and the analog ground.  D/A converter related pin. Connect a capacitor of approximately 0.1μF between this pin and the analog power supply (DAVD).  Reference of this pin and the analog power supply (DAVD).  Sets the full-scale value of the Y and C-channel D/A converter output signal.  Reference of the D/A converter related pin. Connect to the analog ground (DAVS) via a capacitor of approximately 0.1μF.  TEST I Test pin. Normally fix to "Low".  Digital power supply. (5.0V)  Reference of the D/A converter output resistor "R" of the D/A converter) on the pin and the analog ground (DAVS) via a capacitor of approximately 0.1μF.  Test I Test pin. Normally fix to "Low".  Digital ground.  Y/C separation mode setting. MOD2 MOD1  L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5          | ADVD   | _   | A/D converter analog power supply. (5.0V)                                            |

| 7 ACO O Output can be obtained by connecting a resistor between this pin and the analog ground.  8 DAVD — D/A converter analog power supply. (5.0V)  Analog luminance signal output. Output can be obtained by connecting a resistor between this pin and the analog ground.  10 DAVS — D/A converter analog ground.  11 VG O D/A converter related pin. Connect a capacitor of approximately 0.1μF between this pin and the analog power supply (DAVD).  12 VRF I Sets the full-scale value of the Y and C-channel D/A converter output signal.  13 IRF O Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter) D/A converter related pin. Connect to the analog ground (DAVS) via a capacitor of approximately 0.1μF.  15 TEST I Test pin. Normally fix to "Low".  16 DVDD — Digital power supply. (5.0V)  18 DVss — Digital ground.  17 MOD2 I V/C separation mode setting. MOD2 MOD1 L L Adaptive processing mode H L BPF separation mode H | 6          | RT     | 0   | Reference top voltage for the A/D converter (2.60V typ.).                            |

| Analog luminance signal output. Output can be obtained by connecting a resistor between this pin and the analog ground.  DAVS — D/A converter analog ground.  D/A converter related pin. Connect a capacitor of approximately 0.1μF between this pin and the analog power supply (DAVD).  VRF I Sets the full-scale value of the Y and C-channel D/A converter output signal.  RRF O Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter)  Analog luminance signal output.  Output can be obtained by connecting a resistor between this pin and the analog ground.  PAR O D/A converter related pin. Connect to the Y and C-channel D/A converter output signal.  Test pin. Normally fix to "Low".  Test pin. Normally fix to "Low".  Digital power supply. (5.0V)  ROD2 I Y/C separation mode setting. MOD2 MOD1  L L Adaptive processing mode H L BPF separation mode H L BPF separation mode H H Through mode  VEH3 I VEH2 I VEH2 I Vertical enhancement setting.  Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  Vertical ground.  Vertical ground.  Digital ground.  Digital ground.  Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7          | ACO    | 0   | Output can be obtained by connecting a resistor between this pin and the analog      |

| 9 AYO O Output can be obtained by connecting a resistor between this pin and the analog ground.  10 DAVS — D/A converter analog ground.  11 VG O D/A converter related pin. Connect a capacitor of approximately 0.1μF between this pin and the analog power supply (DAVD).  12 VRF I Sets the full-scale value of the Y and C-channel D/A converter output signal.  13 IRF O Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter)  14 VB O D/A converter related pin. Connect to the analog ground (DAVS) via a capacitor of approximately 0.1μF.  15 TEST I Test pin. Normally fix to "Low".  16 DVpp — Digital power supply. (5.0V)  18 DVss — Digital ground.  17 MOD2 I Y/C separation mode setting. MOD2 MOD1  L L Adaptive processing mode H L BPF separation mode H H Through mode Vertical enhancement setting.  20 VEH3 I VeH2 I Vertical enhancement setting.  21 VEH2 I Vertical enhancement setting.  22 VEH1 I Vertical enhancement setting.  23 DVss — Digital ground.  24 DVss — Digital ground.  25 DVss — Digital ground.  26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8          | DAVD   | _   | D/A converter analog power supply. (5.0V)                                            |

| 11 VG O D/A converter related pin. Connect a capacitor of approximately 0.1µF between this pin and the analog power supply (DAVD).  12 VRF I Sets the full-scale value of the Y and C-channel D/A converter output signal.  13 IRF O Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter)  14 VB O D/A converter related pin.  15 TEST I Test pin. Normally fix to "Low".  16 DVDD — Digital power supply. (5.0V)  18 DVss — Digital ground.  17 MOD2 I Y/C separation mode setting. MOD2 MOD1  19 MOD1 I H L Adaptive processing mode  19 H L BPF separation mode  10 VEH3 I Vertical enhancement setting.  21 VEH2 I Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  22 VEH1 I Digital ground.  24 DVss — Digital ground.  25 DVss — Digital ground.  26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9          | AYO    | 0   | Output can be obtained by connecting a resistor between this pin and the analog      |

| this pin and the analog power supply (DAVD).  12 VRF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10         | DAVS   | _   | D/A converter analog ground.                                                         |

| 13 IRF O Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter)  14 VB O D/A converter related pin. Connect to the analog ground (DAVS) via a capacitor of approximately 0.1μF.  15 TEST I Test pin. Normally fix to "Low".  16 DVpb — Digital power supply. (5.0V)  18 DVss — Digital ground.  17 MOD2 I Y/C separation mode setting. MOD2 MOD1 L L Adaptive processing mode H L BPF separation mode H H Through mode  20 VEH3 I Vertical enhancement setting. Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  21 VEH2 I Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  22 VEH1 I Digital ground.  24 DVss — Digital ground.  25 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11         | VG     | 0   |                                                                                      |

| 14 VB O D/A converter related pin. Connect to the analog ground (DAVS) via a capacitor of approximately 0.1μF.  15 TEST I Test pin. Normally fix to "Low".  16 DVpp — Digital power supply. (5.0V)  18 DVss — Digital ground.  17 MOD2 I Y/C separation mode setting. MOD2 MOD1 L L Adaptive processing mode H L BPF separation mode H H Through mode  20 VEH3 I VeH2 I Vertical enhancement setting. Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  21 VEH1 I Digital ground.  23 DVss — Digital ground.  24 DVss — Digital ground.  25 DVss — Digital ground.  26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12         | VRF    | I   | Sets the full-scale value of the Y and C-channel D/A converter output signal.        |

| 14    VB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13         | IRF    | 0   | Connect a resistor of "16R" (16 times the output resistor "R" of the D/A converter). |

| 16 DVpb — Digital power supply. (5.0V)  18 DVss — Digital ground.  17 MOD2   Y/C separation mode setting. MOD2 MOD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14         | VB     | 0   | ·                                                                                    |

| 18 DVss — Digital ground.  17 MOD2   I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15         | TEST   | I   | Test pin. Normally fix to "Low".                                                     |

| 17 MOD2 I Y/C separation mode setting. MOD2 MOD1 L L L Adaptive processing mode H L BPF separation mode H H H Through mode  20 VEH3 I 21 VEH2 I Vertical enhancement setting. Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  22 VEH1 I 23 DVss — Digital ground.  24 DVss — Digital ground.  25 DVss — Digital ground.  26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16         | DVDD   | _   | Digital power supply. (5.0V)                                                         |

| L L Adaptive processing mode H L BPF separation mode H H H Through mode  Vertical enhancement setting. Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  VEH1 I  Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18         | DVss   | _   | Digital ground.                                                                      |

| 19 MOD1 I H H Through mode  20 VEH3 I  21 VEH2 I Vertical enhancement setting. Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  22 VEH1 I Digital ground.  24 DVss — Digital ground.  25 DVss — Digital ground.  26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17         | MOD2   | I   | L L Adaptive processing mode                                                         |

| 21       VEH2       I         22       VEH1       I         23       DVss       —         24       DVss       —         Digital ground.         25       DVss       —         Digital ground.         26       DVss       —         Digital ground.         Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19         | MOD1   | I   |                                                                                      |

| 21 VEH2 I Can be set in 8 stages from VEH3 VEH2 VEH1: LLL (off) to HHH (max.)  22 VEH1 I Digital ground.  23 DVss — Digital ground.  24 DVss — Digital ground.  25 DVss — Digital ground.  26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20         | VEH3   | I   | Vertical enhancement setting                                                         |

| 22 VEH1 I   23 DVss — Digital ground.   24 DVss — Digital ground.   25 DVss — Digital ground.   26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21         | VEH2   | I   |                                                                                      |

| 24 DVss — Digital ground.  25 DVss — Digital ground.  26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22         | VEH1   | I   |                                                                                      |

| 25 DVss — Digital ground.  26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23         | DVss   | _   | Digital ground.                                                                      |

| 26 DVss — Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24         | DVss   | _   | Digital ground.                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25         | DVss   | _   | Digital ground.                                                                      |

| 27 DVDD — Digital power supply. (5.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26         | DVss   | _   | Digital ground.                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27         | DVDD   | _   | Digital power supply. (5.0V)                                                         |

| Pin<br>No. | Symbol | I/O | Description                                                                                                                                                                                              |

|------------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28         | TEST   | I   | Test pin. Normally fix to "Low".                                                                                                                                                                         |

| 29         | DVss   | _   | Digital ground.                                                                                                                                                                                          |

| 30         | APCN   | I   | Horizontal aperture correction circuit setting. Low: Off, High: On.                                                                                                                                      |

| 31         | TRAP   | I   | Trap filter setting. Low: Off, High: On.                                                                                                                                                                 |

| 32         | TEST   | I   | Test pin. Normally open or fix to "Low".                                                                                                                                                                 |

| 33         | TEST   | I   | Test pin. Normally open or fix to "Low".                                                                                                                                                                 |

| 34         | DVDD   | _   | Digital power supply. (5.0V)                                                                                                                                                                             |

| 35         | TEST   | I   | Test pin. Normally open or fix to "Low".                                                                                                                                                                 |

| 36         | DVss   | _   | Digital ground.                                                                                                                                                                                          |

| 37         | FIN    | I   | Clock input. Input the burst-locked fsc (2fsc) when using the internal PLL. Input the burst-locked 4fsc when not using the internal PLL.                                                                 |

| 38         | CKSL   | I   | PLL control. Low: The internal PLL is not used. The clock (4fsc) which is input to FIN is supplied internally. High: The internal PLL is used. VCO oscillation output 4fsc clock is supplied internally. |

| 39         | PLSL   | I   | Selects the clock input to FIN. Low: fsc, High: 2fsc. When inputting 4fsc to FIN (when not using the internal PLL), this pin may be set to either "Low" or "High".                                       |

| 40         | МСКО   | 0   | Clock (4fsc) output.                                                                                                                                                                                     |

| 41         | ADCK   | I   | Clock input for A/D converter. Normally connect to MCKO.                                                                                                                                                 |

| 42         | СРО    | 0   | PLL phase comparator output. Leave open when not using the PLL.                                                                                                                                          |

| 43         | PLVS   | _   | PLL analog ground.                                                                                                                                                                                       |

| 44         | VCV    | I   | VCO control voltage input. Connect to PLVS when not using the PLL.                                                                                                                                       |

| 45         | PLVD   |     | PLL analog power supply. (5.0V)                                                                                                                                                                          |

| 46         | CLVD   |     | Clamp D/A converter analog power supply. (5.0V)                                                                                                                                                          |

| 47         | CLPEN  | I   | Clamp circuit enable pin. Low: Clamp on, High: Clamp off.                                                                                                                                                |

| 48         | CLVS   | _   | Clamp D/A converter analog ground.                                                                                                                                                                       |

#### **Electrical Characteristics**

## **DC Characteristics**

$(VDD = 4.75 \text{ to } 5.25 \text{V}, \text{Vss} = 0 \text{V}, \text{Ta} = -20 \text{ to } +70 ^{\circ}\text{C})$

| Item                         | Symbol   | Measurement conditions | Min.      | Тур. | Max.   | Unit | Applicable pins |

|------------------------------|----------|------------------------|-----------|------|--------|------|-----------------|

|                              | DVDD     |                        |           |      |        |      |                 |

|                              | DAVD     |                        |           |      |        |      |                 |

| Supply voltage               | ADVD     | <u> </u>               | 4.75      | 5.0  | 5.25   | V    | *1              |

|                              | PLVD     |                        |           |      |        |      |                 |

|                              | CLVD     |                        |           |      |        |      |                 |

| Operating temperature        | Topr     | _                      | -20       |      | +70    | °C   |                 |

| Supply current               | IDD      | Clock 14.3MHz          | _         | 85   | 120    | mA   | _               |

| Input/output voltage         | Vı, Vo   | _                      | Vss       |      | VDD    | V    | *2              |

| lanut valtaga                | ViH      | OMOO la saliana t      | 0.7Vpd    |      |        | V    |                 |

| Input voltage                | VIL      | CMOS level input       |           |      | 0.3Vdd | ] V  | *3              |

| Input rise/fall time         | tr, tf   | _                      | 0         |      | 500    | ns   | *1              |

|                              | Vон      | Iон = −2mA             | Vpp – 0.8 |      |        |      | *4              |

| Output voltage               | VOH      | Iон = −3mA             | 0.0       |      |        | V    | *5              |

| Output voltage               | Vol      | IoL = 4mA              |           |      | 0.4    | ]    | *4              |

|                              | VOL      | IoL = 1.5mA            |           |      | 0.4    |      | *5              |

| Clock input amplitude        | VIN      | fmax = 50MHz sine wave | 0.5       |      |        | Vp-p | 11.0            |

| Feedback resistance value    | RfB      | VIN = Vss or VDD       | 250k      | 1M   | 2.5M   | Ω    | *6              |

| Input look ourrent           | IIL, IIH | VIN = Vss or VDD       | -10       |      | 10     |      | *7              |

| Input leak current           | Іін      | VIH = VDD              | 40        | 100  | 240    | μA   | *8              |

| Clock amplifier output delay |          | _                      | 3.0       | 9.0  | 18.0   | ns   | *9              |

<sup>\*1</sup> All pins

<sup>\*2</sup> All pins other than \*6

<sup>\*3</sup> All input pins other than \*6

<sup>\*4</sup> All output pins other than \*5

<sup>\*5</sup> CPO (Pin 42)

<sup>\*6</sup> FIN (Pin 37)

<sup>\*7</sup> All input pins other than \*8

<sup>\*8</sup> Pins 32, 33 and 35

<sup>\*9</sup> MCKO (Pin 40)

# I/O Pin Capacitance

| 1  | Ta =  | 25°C  | f = | 1MHz.    | VIN =   | VOLIT = | = 0\/)  |

|----|-------|-------|-----|----------|---------|---------|---------|

| ١. | 1 a - | ZJ U. | -   | IIVIIIZ. | V 111 — | VOUI -  | – v v i |

| Item                   | Symbol | Min. | Min. | Max. | Unit |

|------------------------|--------|------|------|------|------|

| Input pin capacitance  | Cin    | _    | _    | 9    | pF   |

| Output pin capacitance | Соит   | _    | _    | 11   | Ρ'   |

#### **Internal 8-bit A/D Converter Characteristics**

$(VDD = 5V, Ta = 25^{\circ}C, f = 10MHz)$

| Item                         | Symbol    | Conditions | Min. | Тур. | Max. | Unit |

|------------------------------|-----------|------------|------|------|------|------|

| Resolution                   | n         |            | _    | 8    | _    | bit  |

| Max. conversion speed        | fmax      |            | 14.3 | _    | _    | MSPS |

| Analog input bandwidth       | BW        | -3dB       | _    | 18   | _    | MHz  |

| 0 1/1                        | VRB       |            | 0.48 | 0.52 | 0.56 | V    |

| Self bias                    | VRT – VRB |            | 1.96 | 2.08 | 2.22 | V    |

| Output data delay            | tpd       |            | _    | _    | 45   | ns   |

| Differential linearity error | Ed        |            | -1.0 | _    | +1.0 | LSB  |

| Integral linearity error     | EL        |            | -2.0 | _    | +2.0 | LSB  |

#### **Internal 8-bit D/A Converter Characteristics**

(VDD = 5V, VRF = 2V, RIRF =  $3.3k\Omega$ , R =  $200\Omega$ , Ta =  $25^{\circ}$ C, f = 10MHz)

| Item                         | Symbol | Conditions                    | Min.  | Тур. | Max.  | Unit |

|------------------------------|--------|-------------------------------|-------|------|-------|------|

| Resolution                   | n      |                               | _     | 8    | _     | bit  |

| Max. conversion speed        | fmax   |                               | 14.3  | _    | _     | MSPS |

| Differential linearity error | Ed     |                               | -0.8  | _    | +0.8  | LSB  |

| Integral linearity error     | EL     |                               | -2.0  | _    | +2.0  | LSB  |

| Output full-scale voltage    | VFS    |                               | 1.805 | 1.90 | 1.995 | V    |

| Output full-scale current    | IFS    |                               | _     | 9.5  | 15    | mA   |

| Output offset voltage        | Vos    |                               | _     | _    | 1.0   | mV   |

| Glitch energy                | GE     | $R = 75\Omega$ , 1Vp-p output | _     | 30   | _     | pV-s |

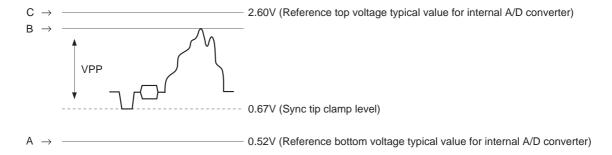

# **Internal Clamp**

$(VDD = 5V, Ta = 25^{\circ}C, f = 10MHz)$

| Item           | Symbol | Conditions | Min. | Тур. | Max. | Unit |

|----------------|--------|------------|------|------|------|------|

| Clamp level *1 | CLV    |            |      | 0.67 |      | V    |

<sup>\*1</sup> Sync tip clamp

#### **Description of Functions**

#### • Y/C separation mode

The Y/C separation mode can be switched by the following pin settings.

| Mode name                | MOD2 (Pin 17) | MOD1 (Pin 19) |

|--------------------------|---------------|---------------|

| Adaptive processing mode | L             | L             |

| BPF separation mode      | Н             | L             |

| Through mode             | Н             | Н             |

#### Adaptive processing mode:

Y/C separation is performed by detecting the correlation between three lines and switching between comb filter and BPF processing.

#### BPF separation mode:

Y/C separation is performed only by BPF processing.

#### Through mode:

The composite video signal input from ADIN (Pin 2) is A/D converted and then D/A converted without modification. D/A outputs are AYO (Pin 9) and ACO (Pin 7).

#### Horizontal aperture correction circuit

This circuit corrects the frequency response degradation caused by the aperture effects accompanying D/A conversion. This circuit is valid in the adaptive processing and BPF separation modes noted above.

#### Trap filter circuit

A trap filter is applied to remove the frequency components near fsc in the luminance signal after Y/C separation.

This reduces the fsc frequency component gain by approximately 2.5dB.

This circuit is valid in the adaptive processing and BPF separation modes noted above.

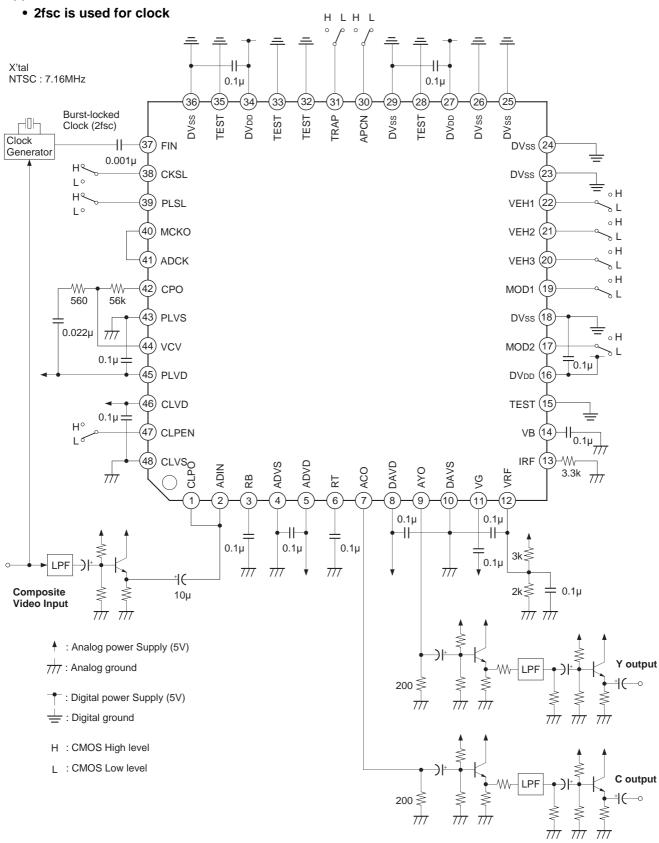

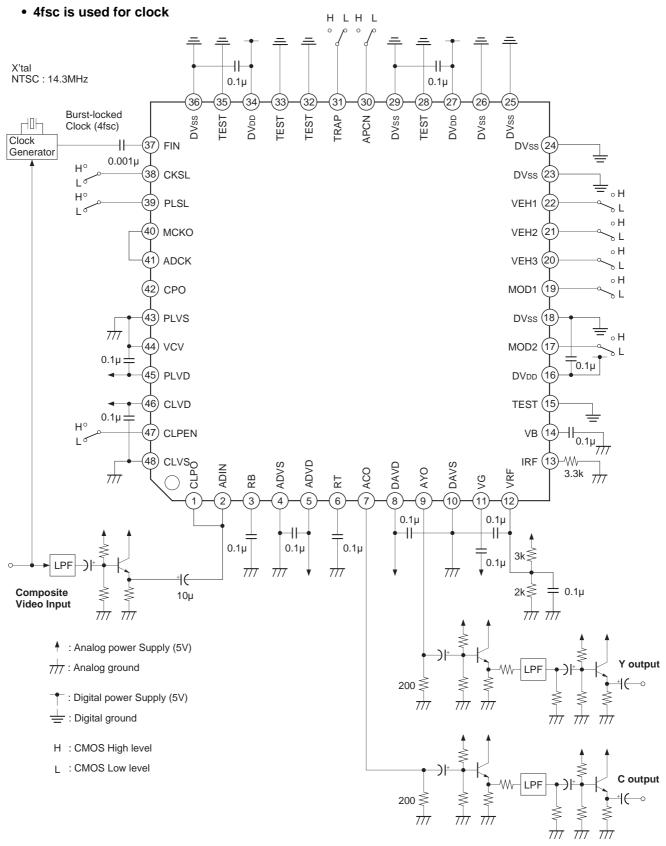

#### • Using the internal PLL (clock selection method)

|              | FIN (Pin 37) | CKSL (Pin 38) | PLSL (Pin 39) |

|--------------|--------------|---------------|---------------|

| DLL upod     | fsc input    | Н             | L             |

| PLL used     | 2fsc input   | Н             | Н             |

| PLL not used | 4fsc input   | L             | L/H           |

#### · Vertical enhancement circuit

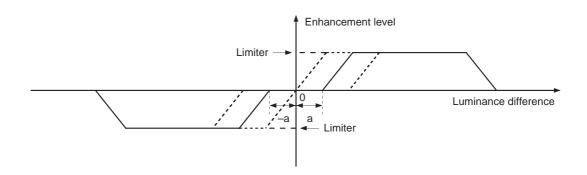

This circuit generates an enhanced component in accordance with the vertical aperture component (luminance difference from the preceding and following lines) of the luminance signal. The vertical aperture of the picture can be enhanced naturally by adding this enhanced component to the luminance signal after Y/C separation.

The enhancement level can be set in eight steps. The size of | a | in the figure below varies according to the pin settings. Accordingly, enhanced level can be changed for portions of natural pictures with small luminance differences where the effects are particularly easy to see.

Portions with large luminance differences are cut with a limiter so that they are not excessively enhanced. Also, portions with extremely large luminance differences such as white and black lines are not enhanced because they need be enhanced any more.

| Enhancement | Pin settings     |                  |                  |              |

|-------------|------------------|------------------|------------------|--------------|

| level       | VEH3<br>(Pin 20) | VEH2<br>(Pin 21) | VEH1<br>(Pin 22) | a            |

| OFF         | L                | L                | L                |              |

| 1           | L                | L                | Н                | Large        |

| 2           | L                | Н                | L                | <b>↑</b>     |

| 3           | L                | Н                | Н                |              |

| 4           | Н                | L                | L                |              |

| 5           | Н                | L                | Н                |              |

| 6           | Н                | Н                | L                | $\downarrow$ |

| Max         | Н                | Н                | Н                | Small        |

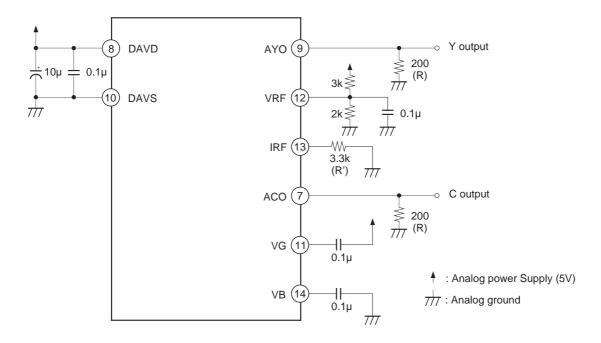

## **Application Circuit for D/A Converter Block**

#### Method of selecting the output resistor

The CXD2093Q has a built-in current output type D/A converter. To obtain the output voltages, connect resistors to the AYO and ACO pins.

The specs are as follows: output full-scale voltage VFS = 0.5 to 2.0 [V], output full-scale current IFS = 0 to 15 [mA].

Calculate the output resistance value using the relationship  $V_{FS} = I_{FS} \times R$ . In addition, connect a resistor of 16 times the output resistor to the reference current pin (IRF). In case this results in a unpractical value, use a resistance value as close to the calculated value as possible.